国際会議The 19th IEEE Workshop on RTL and High Level Testing (WRTLT2018)が2018年10月18~19日に中国・合肥・Westin Hotel Baohe Hefeiで開催され,数理情報工学専攻の大学院博士前期課程1年の石山悠太さん(細川研究室所属)の論文 " A Controller Augmentation Method for k-cycle Capture Test Generation Using Partial Scan Designs” と,大学院博士前期課程1年の竹内勇希さん(細川研究室所属)の論文" A Design for Testability Method to Improve Transition Fault Coverage Using Controller Augmentation at Register Transfer Level"が採択され,発表しました.

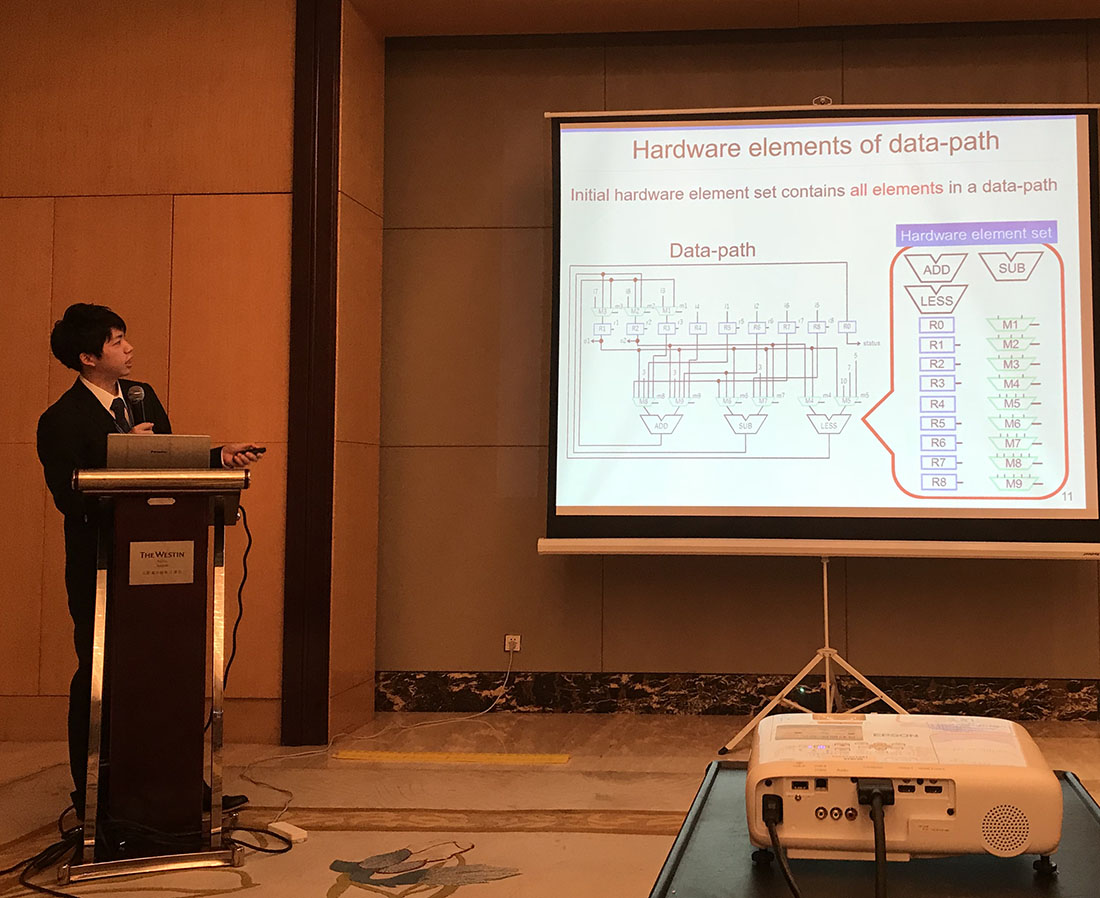

石山さんの発表内容は,デジタル情報機器に搭載されているシステムLSI(大規模集積回路)のテスト容易化設計に関するものです.具体的にはコントローラと呼ばれる状態遷移機械でモデル化されたハードウェア中のレジスタを可制御・可観測にし,さらにデータパスの中の演算器などのハードウェア要素がkサイクル間で容易にテストできるように,コントローラの無効状態と呼ばれる空間にテスト可能な制御信号を出力するコントローラ拡大という手法を提案しました。この研究内容は株式会社ソシオネクスト社(富士通とパナソニックのLSI設計部門が母体となって設立された会社)との共同研究によるものです.

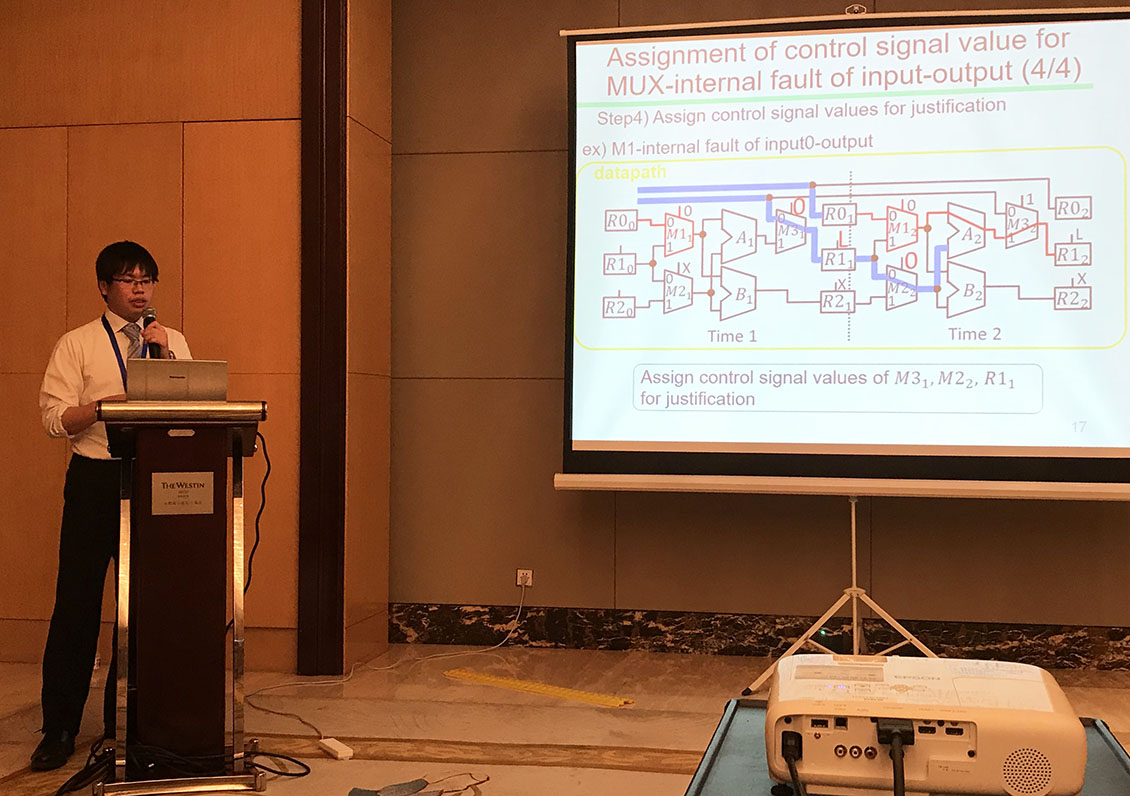

竹内さんの発表内容は,システムLSIの遷移故障と呼ばれるタイミング欠陥をモデル化した故障の検出率を向上させるためのテスト容易化設計に関するものです.具体的には,コントローラから生成される制御信号で検出不能なデータパス中のマルチプレクサやレジスタの故障をテストできるように,コントローラ拡大手法を提案しました.その結果,データパス中の遷移故障検出率を3.7%向上させることができました.