国際会議The 17th IEEE Workshop on RTL and High Level Testing (WRTLT2016)が2016年11月24~25日に日本・広島・安芸グランドホテルで開催され,数理情報工学専攻の大学院博士前期課程1年の佐藤護さん(細川研究室所属)の論文 "A Binding Method to Generate Easily Testable Functional Time Expansion Models“と,大学院博士前期課程1年の武田俊さん(細川研究室所属)の論文" A Design for Testability Method at RTL for Concurrent Operational Unit Testing "が採択され,発表しました.

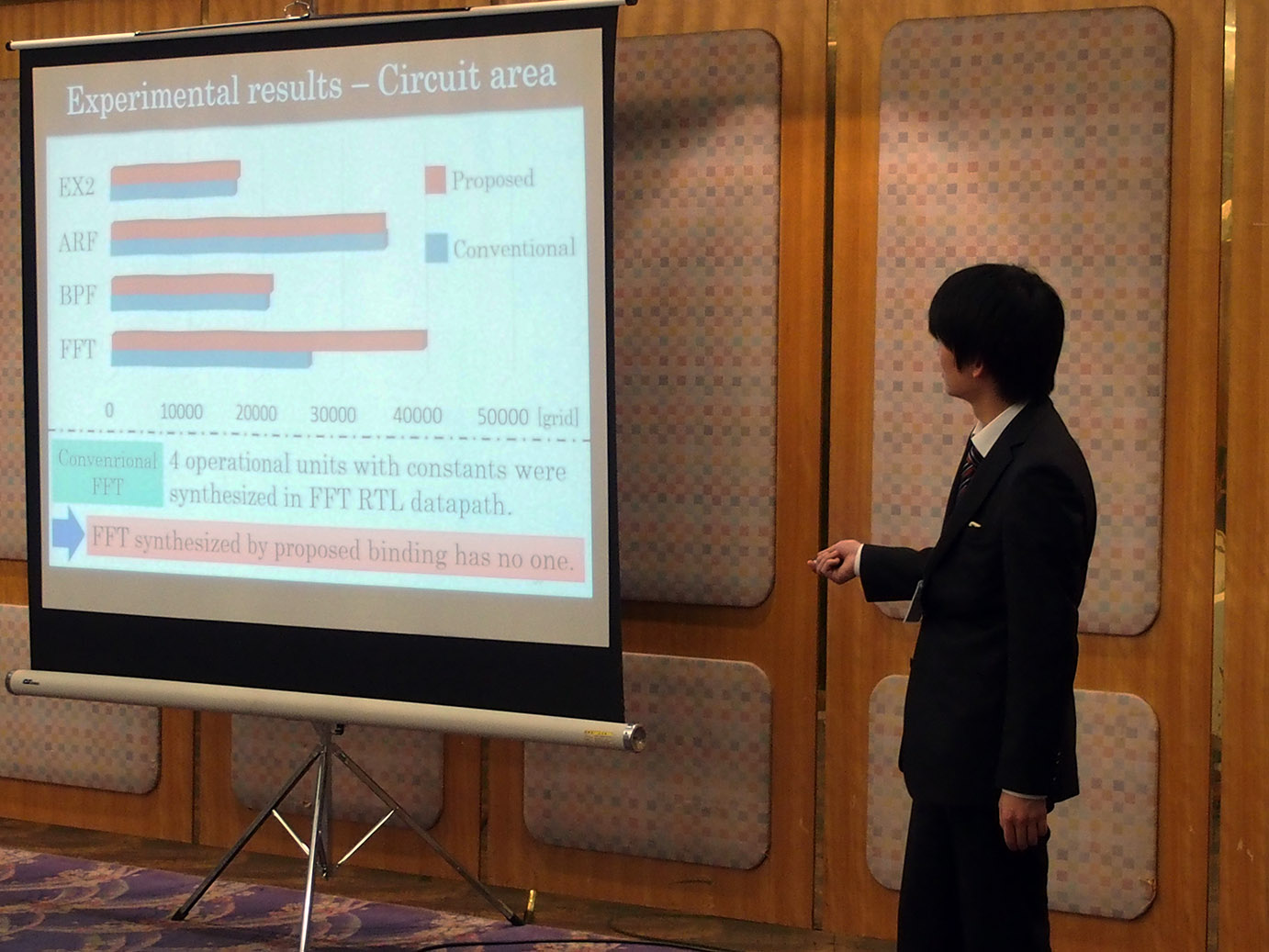

佐藤さんの発表内容は,デジタル情報機器に搭載されているシステムLSI(大規模集積回路)の動作記述(C言語など)からテスト容易なレジスタ転送レベル回路(Verilog-HDLなど)を合成するアルゴリズムに関するものです.システムLSIは製造後にその品質を保証するためにテストを行う必要があります.ハードウェアの各要素は外部入力や外部出力に近いほうが,その際に使用する0と1の値で構成されるテストパターンの系列を容易に生成することができます.合成時にハードウェアの演算器の入力は外部入力から近い経路を、演算器の出力は外部出力に近い経路を生成するアルゴリズムを提案しました.実験では,このテスト容易化動作合成アルゴリズムを適用して生成された回路に存在する演算器の入出力はすべて外部入力と外部出力へレジスタ1個のみ介して到達できる経路を生成できたことを示しました.

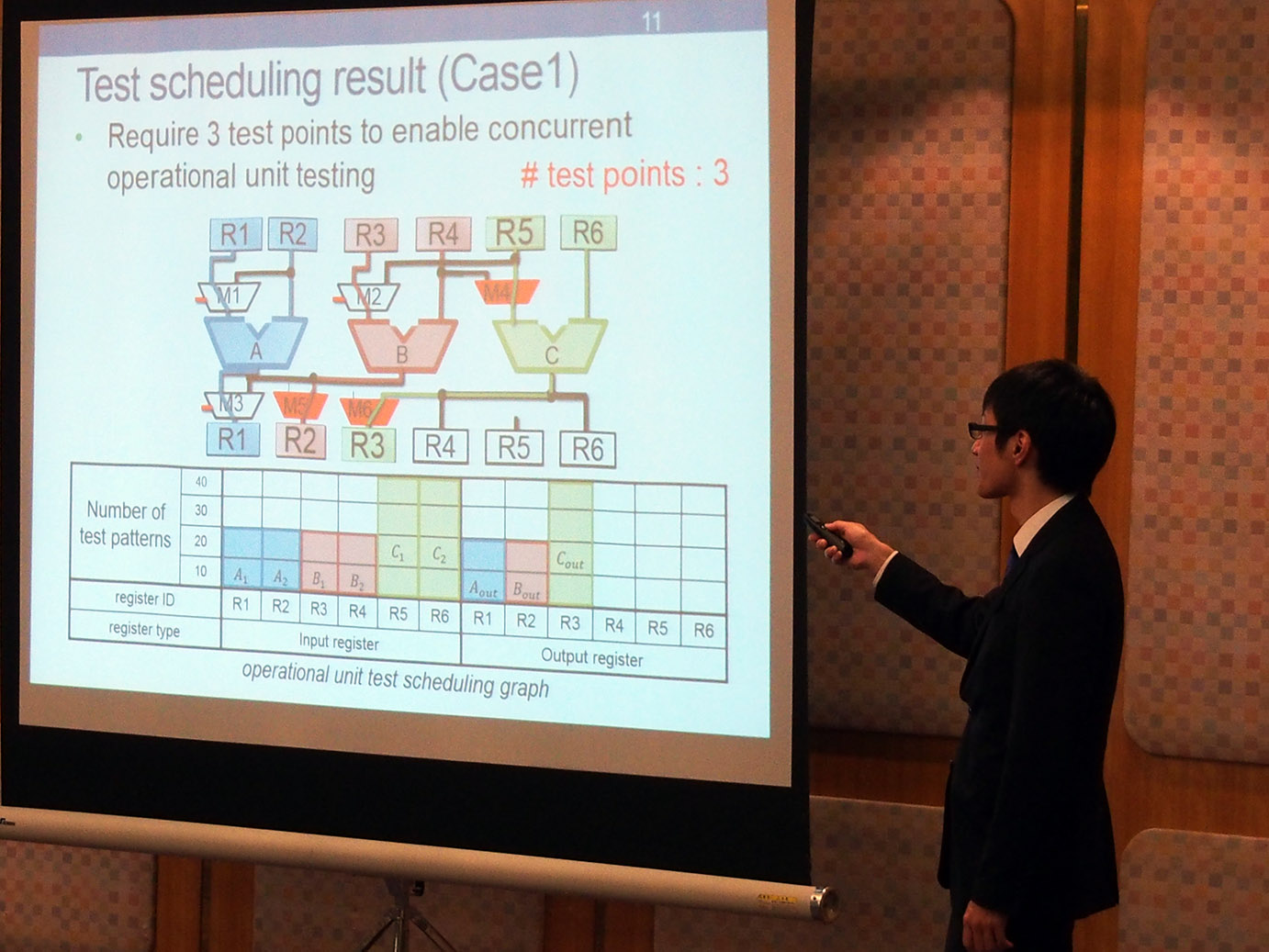

武田さんの発表内容は,システムLSIのレジスタ転送レベルのテスト容易化設計に関するものです.システムLSIの製造後のテストでは,低コストで高品質なテストパターンが要求されます.ハードウェアの大部分を占める演算器を同時にテストし,テストコストに直結するテストパターン数を削減するためのテスト容易化設計手法を提案しました.具体的にはコントローラと呼ばれる有限状態遷移機械の拡大を行い,テストパターン数を従来技術と比較して20%削減できることを示しました.