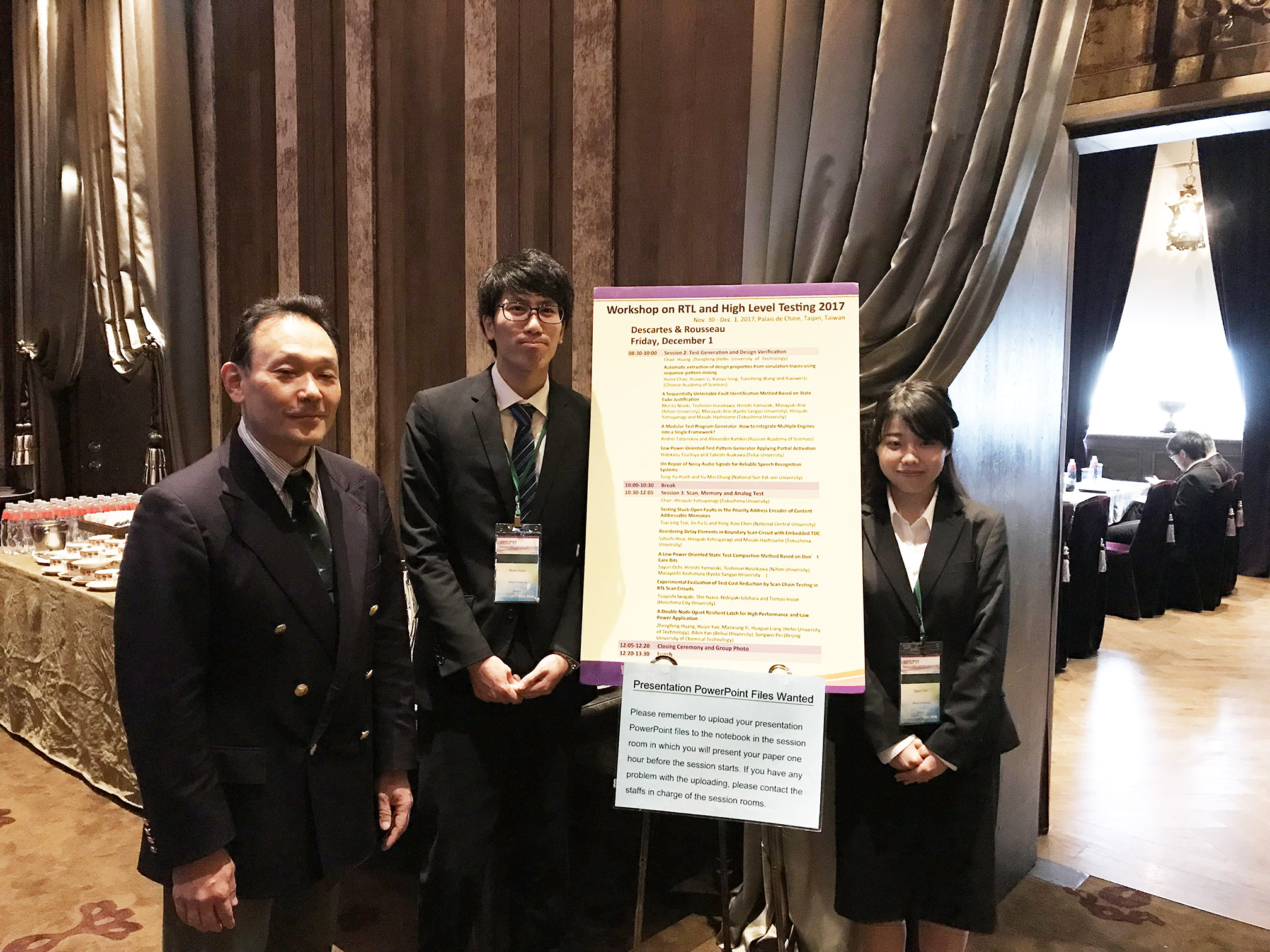

国際会議The 18th IEEE Workshop on RTL and High Level Testing (WRTLT2017)が2017年11月30~12月1日にTaiwan・Taipei・Palais de Chine Hotelで開催され,数理情報工学専攻の大学院博士前期課程2年の二関森人さん(細川研究室所属)の論文 " A Sequentially Untestable Fault Identification Method Based on State Cube Justification“と,大学院博士前期課程1年の越智小百合さん(細川研究室所属)の論文" A Low Power Oriented Static Test Compaction Method Based on Don’t Care Bits"が採択され,発表しました.

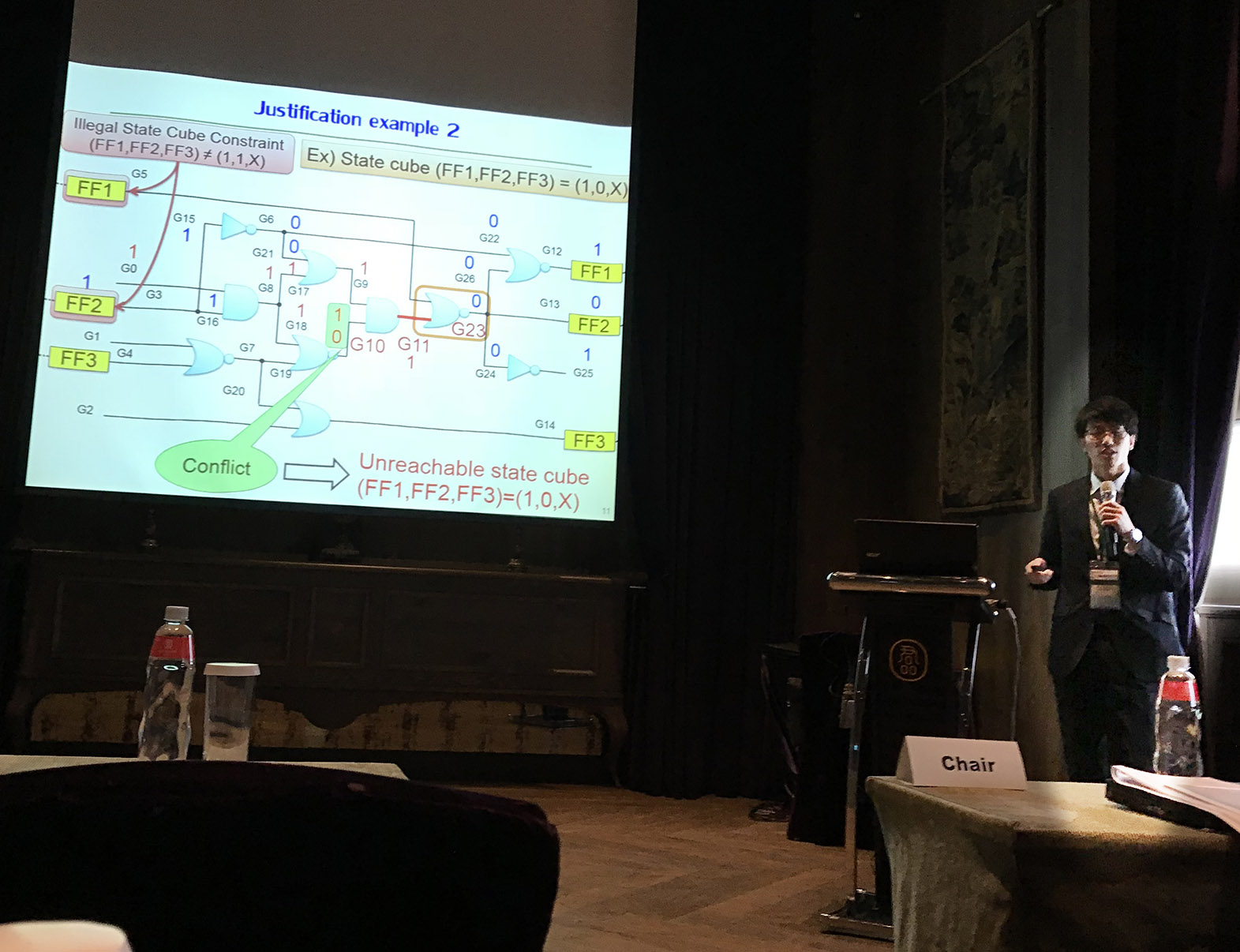

二関さんの発表内容は,デジタル情報機器に搭載されているシステムLSI(大規模集積回路)のテスト不能故障判定アルゴリズムに関するものです.システムLSIである順序回路中にはテストができない故障(テスト不能故障)が存在しますが,これらの故障を効率よく判定するアルゴリズムが必要です.二関さんの研究はSAT(充足可能性問題)ソルバーを用いて順序回路中に存在する初期状態から到達不可能な状態キューブを判定し,その情報を用いてテスト不能故障を判定するためのアルゴリズムを提案しました.その結果,ITC’99ベンチマーク回路のテスト不能故障数を従来技術と比較して10~107%多く判定できることを示しました.

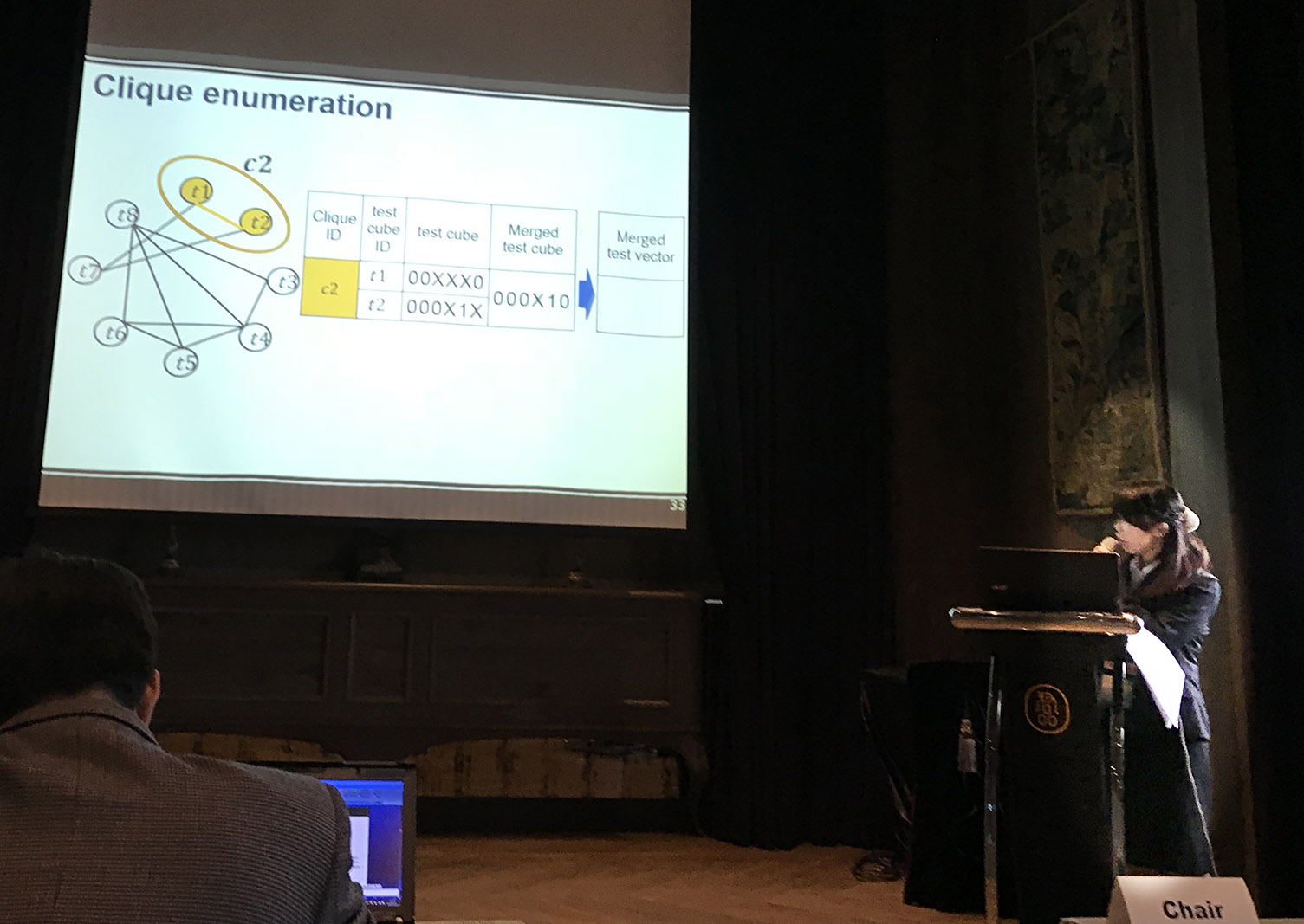

越智さんの発表内容は,システムLSIの低消費電力テスト及びテストコスト削減に関するもので,低消費電力なテストパターン集合から0でも1でもどちらでもよい値であるドントケアを判定し,そのドントケアを用いて低消費電力指向テストパターン圧縮問題を無向グラフにおける最小クリーク被覆問題に帰着させて解くアルゴリズムを提案しました.高消費電力な状態でシステムLSIをテストすると,不良品を良品と判定する誤テストを引き起こすことになります.提案したアルゴリズムを用いてテストパターン圧縮を行うと,高消費電力なテストパターンを生成することなく低消費電力なテストパターン数を平均20%削減することができました.