国際会議The 15th IEEE Workshop on RTL and High Level Testing (WRTLT2014, IEEEの主催で2014年11月19・20日に中国・杭州・Hangzhou Jinxi Hotelで開催)で,数理情報工学専攻の大学院博士前期課程2年の平井淳士さん(細川研究室所属)の論文 "A Simulation Based Low Capture Power Test Generation Method Using Capture Safe Test Vectors "と大学院博士前期課程2年の西間木淳さん(細川研究室所属)の論文"A Scheduling Method for Hierarchical Testability Using Results of Test Environment Generation"が採択され,発表しました.

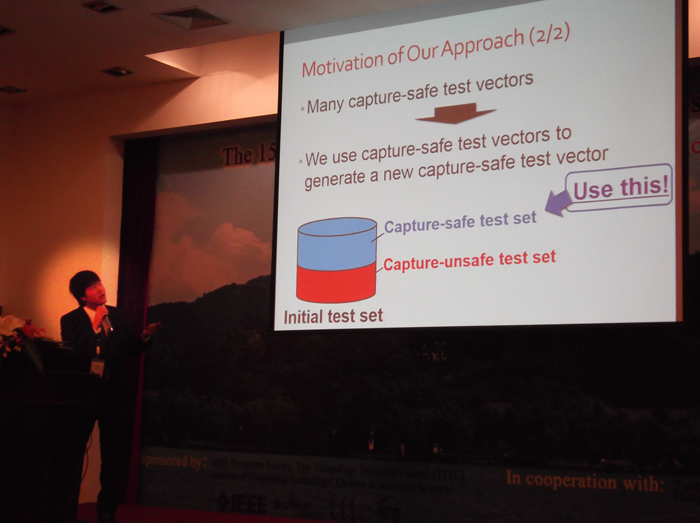

平井さんの発表内容は,デジタル情報機器に搭載されているシステムLSI(大規模集積回路)の低消費電力テストに関するもので,低消費電力なテストパターン集合からデータマイニングしたテストパターンと故障を検出する決定論的なテストパターンを融合し,低消費電力な状態で故障を検出するテストパターンを合成するアルゴリズムに関するものです.高消費電力な状態でシステムLSIをテストすると,不良品を良品と判定する誤テストを引き起こすことになります.提案したアルゴリズムを用いると従来手法と比較し,最大300倍高速に低消費電力な状態で故障を検出するテストパターンを生成することができました.

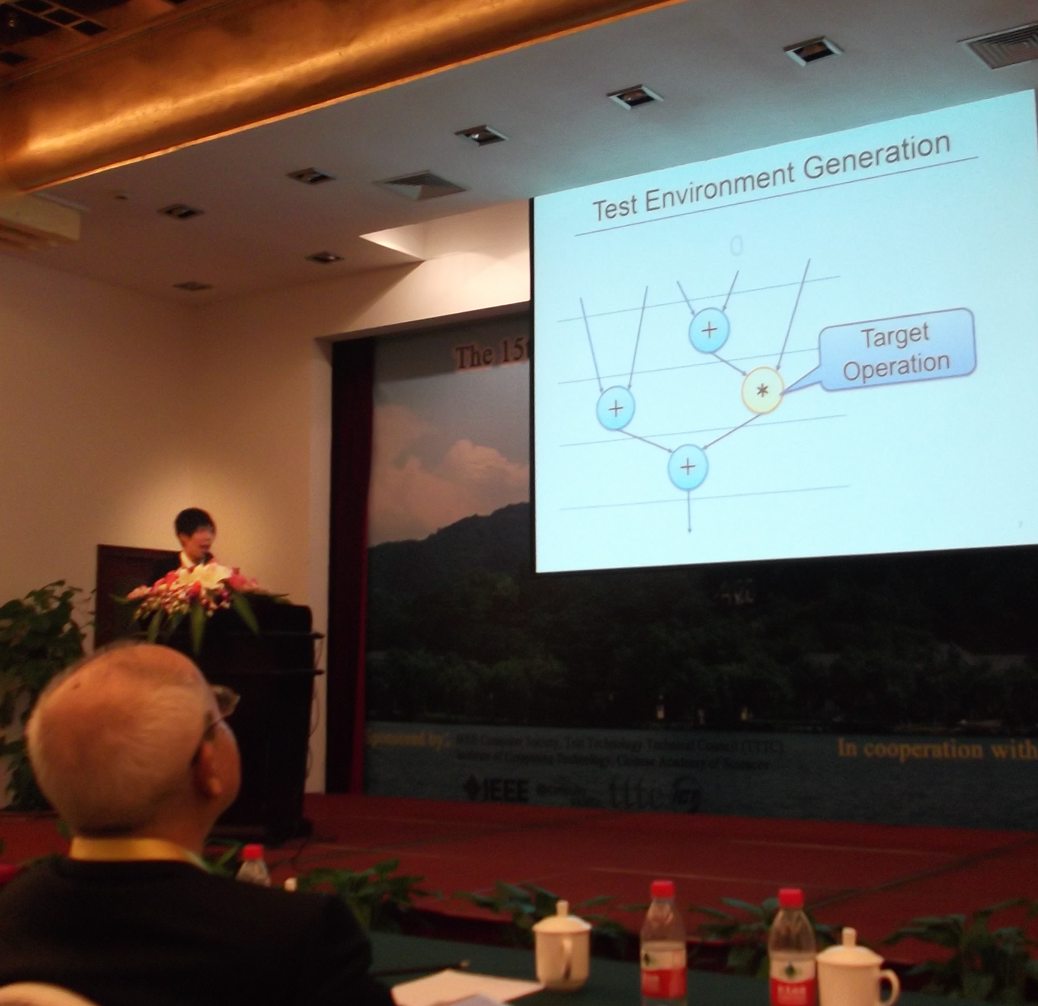

西間木さんの発表内容は,システムLSIの上流設計工程で,テストパターンの生成が容易になるようにテスト容易化を考慮した動作合成アルゴリズムに関するものです.動作合成とは,C言語など を用いてハードウェアの動作を記述したものからレジスタ転送レベル回路を生成するソフトウェアです.西間木さんは昨年度も国際会議で発表しており,その時に動作合成の中のバインディングという動作記述の変数や演算をレジスタや演算器に割当てる処理についてテスト容易化を考慮して行うアルゴリズムを提案しました.今年度は,そのバインディングの効率を高めるためのスケジューリングという演算を実行する時刻を決定する処理についてテスト容易化を考慮したアルゴリズムを提案しました.テスト容易化を考慮した回路を合成することに より,テスト品質の評価尺度である故障検出率が大幅に向上したことを示しました.